# ibaFOB-R

# Reflective Memory Interface Board

Manual Issue1.0

> Measurement Systems for Industry and Energy www.iba-ag.com

#### Manufacturer

iba AG Koenigswarterstraße 44 90762 Fuerth Germany

#### Contacts

| Headquarters | +49 911 97282-0  |

|--------------|------------------|

| Support      | +49 911 97282-14 |

| Engineering  | +49 911 97282-13 |

| E-Mail       | iba@iba-ag.com   |

| Web          | www.iba-ag.com   |

This manual must not be circulated or copied, or its contents utilized and disseminated, without our express written permission. Any breach or infringement of this provision will result in liability for damages.

©iba AG 2024, All rights reserved

The content of this publication has been checked for compliance with the described hardware and software. Nevertheless, deviations cannot be excluded completely so that the full compliance is not guaranteed. However, the information in this publication is updated regularly. Required corrections are contained in the following regulations or can be downloaded on the Internet.

The current version is available for download on our web site http://www.iba-ag.com.

| lssue | Date    | Revision    | Author | Version<br>HW/FW |

|-------|---------|-------------|--------|------------------|

| 1.0   | 09-2024 | First issue | CV, st | 1.0              |

Windows<sup>®</sup> is a label and registered trademark of the Microsoft Corporation. Other product and company names mentioned in this manual can be labels or registered trademarks of the corresponding owners.

#### Certification

The product is certified according to the European standards and directives. This product meets the general safety and health requirements.

Other international and national standards were observed.

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

## Contents

| 1  | About t   | this documentation6                     |

|----|-----------|-----------------------------------------|

|    | 1.1       | Target group6                           |

|    | 1.2       | Notations6                              |

|    | 1.3       | Used symbols7                           |

| 2  | About i   | baFOB-R8                                |

|    | 2.1       | Features9                               |

|    | 2.2       | PCI Express Compliance9                 |

|    | 2.3       | Vendor and Device identification9       |

| 3  | Safety i  | nstructions                             |

|    | 3.1       | Intended use                            |

|    | 3.2       | Special safety instructions10           |

| 4  | Scope o   | of delivery11                           |

| 5  | System    | requirements                            |

| 6  | Installir | ng and removing the board13             |

|    | 6.1       | Installing the board13                  |

|    | 6.2       | Removing the board14                    |

| 7  | Descrip   | tion15                                  |

|    | 7.1       | Front view15                            |

|    | 7.2       | Top view                                |

|    | 7.3       | Display elements                        |

|    | 7.4       | Fiber optic connections17               |

| 8  | Configu   | ıration18                               |

|    | 8.1       | Switch S1 configuration                 |

|    | 8.2       | Switch S2 configuration19               |

|    | 8.2.1     | Important remarks before installation20 |

| 9  | Configu   | ıration in ibaPDA21                     |

| 10 | System    | integration                             |

|    | 10.1      | Basic functionality and operation       |

|    | 10.2      | ibaFOB-R hardware registers             |

|    |           |                                         |

| 12 | Support  | and contact                         | .51  |

|----|----------|-------------------------------------|------|

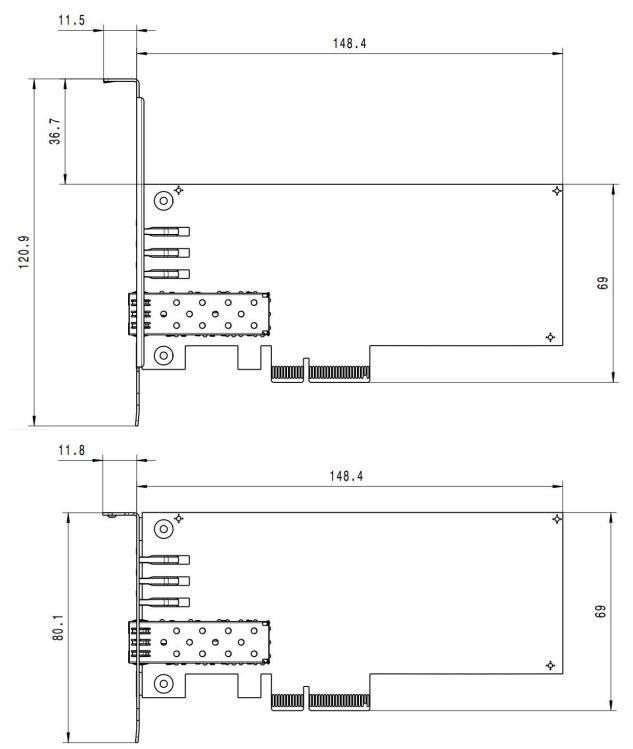

|    | 11.1     | Dimensions                          | . 50 |

| 11 | Technica | l data                              | .49  |

|    | 10.8.3   | RFM Control and Status Registers    |      |

|    | 10.8.2   | Local Configuration Registers       | . 35 |

|    | 10.8.1   | PCI Configuration Registers         | . 27 |

|    | 10.8     | Programming requirements            | . 26 |

|    | 10.7     | Rogue Packet Removal Operation mode | . 25 |

|    | 10.6     | Redundant Transfer mode             | . 25 |

|    | 10.5     | Network interrupts                  | . 25 |

|    | 10.4     | Interrupt generation                | .23  |

|    | 10.3     | Reflective Memory RAM on ibaFOB-R   | . 23 |

## **1** About this documentation

This documentation describes the design, application and operation of the device *ibaFOB-R*.

## 1.1 Target group

This documentation is aimed at qualified professionals who are familiar with handling electrical and electronic modules as well as communication and measurement technology. A person is regarded as professional if he/she is capable of assessing safety and recognizing possible consequences and risks on the basis of his/her specialist training, knowledge and experience and knowledge of the standard regulations.

## 1.2 Notations

In this manual, the following notations are used:

| Action                        | Notation                                                                      |

|-------------------------------|-------------------------------------------------------------------------------|

| Menu command                  | Menu <i>Logic diagram</i>                                                     |

| Calling the menu command      | Step 1 – Step 2 – Step 3 – Step x                                             |

|                               | Example:<br>Select the menu <i>Logic diagram – Add – New function block</i> . |

| Кеуѕ                          | <key name=""></key>                                                           |

|                               | Example: <alt>; <f1></f1></alt>                                               |

| Press the keys simultaneously | <key name=""> + <key name=""></key></key>                                     |

|                               | Example: <alt> + <ctrl></ctrl></alt>                                          |

| Buttons                       | <key name=""></key>                                                           |

|                               | Example: <ok>; <cancel></cancel></ok>                                         |

| Filenames, paths              | Filename, Path                                                                |

|                               | Example: Test.docx                                                            |

## 1.3 Used symbols

If safety instructions or other notes are used in this manual, they mean:

Danger!

The non-observance of this safety information may result in an imminent risk of death or severe injury:

Observe the specified measures.

#### Warning!

The non-observance of this safety information may result in a potential risk of death or severe injury!

Observe the specified measures.

#### Caution!

The non-observance of this safety information may result in a potential risk of injury or material damage!

Observe the specified measures

#### Note

A note specifies special requirements or actions to be observed.

#### Тір

Tip or example as a helpful note or insider tip to make the work a little bit easier.

#### Other documentation

Reference to additional documentation or further reading.

## 2 About ibaFOB-R

The *ibaFOB-R* board is a PCI Express (PCIe) member of the iba family of fiber optic boards. The board supports both low profile and standard height PCIe slots.

The *ibaFOB* board is network compatible with other Reflective Memory products working on 2.125 Gbaud.

Two or more *ibaFOB* boards, along with other members of the Reflective Memory family, can be integrated into a network using standard fiber-optic cables. Each board in the network is referred to as a "node".

Reflective Memory allows computers, workstations, PLCs and other embedded controllers with different architectures and dissimilar operating systems to share data in real time. *ibaFOB-R* is fast, flexible and easy to operate.

Data is transferred by writing to local RAM memory, which appears to reside globally in all boards on the network.

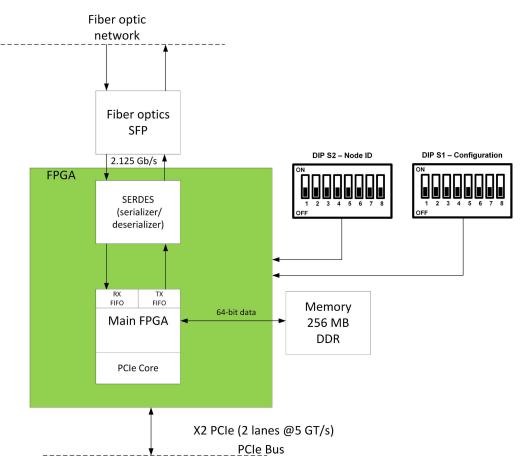

On-board circuitry automatically performs the data transfer to all other nodes with little or no involvement of any host processor. A block diagram of the *ibaFOB-R* board is shown in the following figure.

### 2.1 Features

The features of *ibaFOB-R* board include:

- High speed, easy to use fiber-optic network (2.125 Gbaud serially)

- PCI Express interface (up to 2 active lanes over a 4x connector, speed up to Gen2)

- No host processor involvement in the operation of the network

- Up to 256 nodes

- Up to 500 m on 50/125 µm multimode fiber, 300 m on 62.5/125 µm multimode fiber

- Dynamic packet size, 4 to 64 bytes of payload data per packet

- Fiber network transfer rate 40 MB/s to 162 MB/s

- 256 MB Reflective Memory

- Independent Direct Memory Access (DMA) channel

- Four general purpose network interrupts; each with 32 bits of data

- Selectable PCI PIO window size (2 MB, 16 MB, 64 MB, 256 MB)

- RoHS compliant

### 2.2 PCI Express Compliance

The *ibaFOB-R* board is designed to interface with any suitable PCIe compliant motherboard using a PCIe 4x slot connector (or larger). The *ibaFOB-R* board complies with requirements of the PCI Express Specification, Revision 2.1.

## 2.3 Vendor and Device identification

The PCI Configuration register reserved for the Vendor ID has the value of 0x167F, which designates iba AG.

The PCI Configuration register reserved for the Device ID has the value of 0x5565. The value indicates the iba AG board type for this board and also indicates the Reflective Memory family type.

## 3 Safety instructions

Observe the following safety instructions for *ibaFOB-R*.

## 3.1 Intended use

The device is an electrical apparatus. It must only be used for the following applications:

- Automation of industrial plants

- Measurement data acquisition and analysis

- Applications of iba software products (*ibaPDA*)

The use of the *ibaFOB-R* board in third-party systems is only possible after consultation with iba AG.

## **3.2** Special safety instructions

#### Danger from electric shock!

Disconnect the power supply from the computer before opening the device to avoid an electric shock!

Do not install or remove the card while the power supply is switched on.

#### Caution!

Electrostatic discharges can damage the board! To avoid electrostatic ESD damage, discharge your body electrically before touching the electronic board.

You can discharge your body by touching a conductive, grounded object immediately before working with the board (e.g. metal cabinet components, socket protective conductor contact).

## 4 Scope of delivery

After having unpacked the delivery, please check it for completeness and possible damage. The scope of delivery comprises:

- *ibaFOB-R* board with standard bracket installed

- A multimode SFP module installed

- Low profile bracket to replace the standard bracket to install the board in low profile PCIe slots

For more accessories not included in the delivery (such as FO cables), please see www.iba-ag.com.

## 5 System requirements

Observe the following requirements for using the *ibaFOB-R* board.

#### Hardware

Windows computer with the following minimum configuration:

- Pentium IV/3 GHz

- At least one free PCIe 2.0-x4 compatible slot

- 4 GByte RAM

- Free disk space > 10 GByte

For more information about iba industrial computer, please see www.iba-ag.com.

#### Software

■ *ibaPDA* version 8.8 or higher

## 6 Installing and removing the board

Observe the following warnings when working with the board.

#### Danger from electric shock!

Disconnect the power supply from the computer before opening the device to avoid an electric shock!

Do not install or remove the card while the power supply is switched on.

#### **Caution!**

Electrostatic discharges can damage the board! To avoid electrostatic ESD damage, discharge your body electrically before touching the electronic board.

You can discharge your body by touching a conductive, grounded object immediately before working with the board (e.g. metal cabinet components, socket protective conductor contact).

## 6.1 Installing the board

- 1. Shut down the PC.

- 2. Unplug the mains power line and open the PC so you can reach the PCIe slots.

- 3. Take the board carefully out of the package. Use a grounding cable or discharge any electrostatic charge before taking the board.

- 4. Grab the board at the front plate and the rear upper corner. Do not touch the contacts. Set the S1 and S2 switches as explained in chapter **7** *Configuration*, page 18.

- 5. The *ibaFOB-R* is a low profile form factor board.

The board is shipped assembled with a full-height bracket. A low profile bracket is included in the package. If your computer requires a low profile board, replace the full-height bracket on the board with the supplied low profile bracket.

- 6. Plug in the board carefully into a free PCIe slot and fix the board to the housing of the PC.

- 7. Close the PC.

- 8. Plug in the power line and start the PC.

## 6.2 Removing the board

- 1. Shut down the PC.

- 2. Unplug the mains power line and open the PC so you can reach the PCIe slots.

- 3. Disconnect all external connections from the board.

- 4. Release the fixing screw.

- 5. Unplug the board carefully out of the slot. Store the board in an appropriate container.

## 7 Description

Here you will find views and descriptions of the *ibaFOB-R* board.

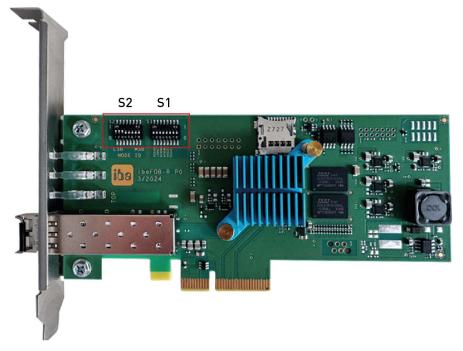

### 7.1 Front view

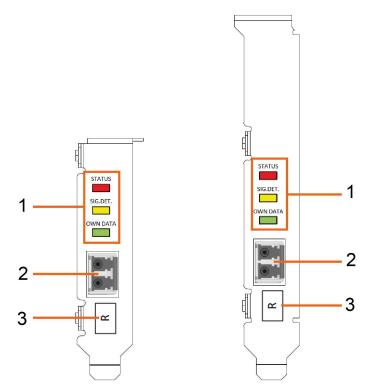

Left: *ibaFOB-R* board with low profile bracket, right: *ibaFOB-R* board with standard bracket

- 1 Operating status indicators

- 2 Fiber optic connection (SFP)

- 3 Identifier for boards of the ibaFOB family

The identifier (3) is used to distinguish the individual ibaFOB board types. The following identifier stands for the following board types:

- D ibaFOB-D and ibaFOB-Dexp

- **TDC** ibaFOB-TDC and ibaFOB-TDCexp

- **SD** ibaFOB-SD and ibaFOB-SDexp

- PC ibaFOB-PlusControl

- R ibaFOB-R

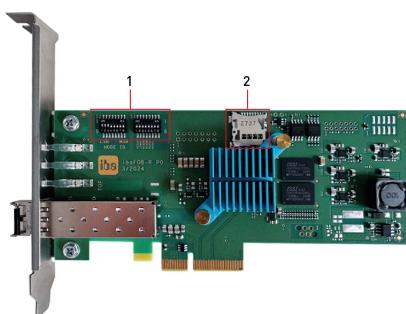

## 7.2 Top view

- 1 DIP switches, see also chapter **7** Configuration, page 18

- 2 SD slot, for service purposes only

## 7.3 Display elements

The operating status of the device is shown by colored status LEDs.

| LED           | Color   | Description                                                                                                                  |  |  |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Status        | Red/off | User defined status indicator. Controlled by the host. Can be set to blinking by <i>ibaPDA</i> – I/O Manager                 |  |  |  |

|               | Blue    | The host system has disabled the board on the PCIe bus.<br>(The board is in PCI Power Management state D3 or kept in Reset.) |  |  |  |

| Signal Yellow |         | Valid optical signal detected on the optical network connection                                                              |  |  |  |

| Detect        | Blue    | Invalid optical signal detected on the optical network connection                                                            |  |  |  |

|               | off     | No optical signal detected on the optical network connection                                                                 |  |  |  |

| Own Data      | Green   | Indicates when own transmitted packets are received back                                                                     |  |  |  |

The Status LED's power up default state is ON.

The Status LED is a user defined board indicator and can be toggled ON or OFF by writing to Bit 31 of the Control and Status register.

The Signal Detect LED turns ON if the receiver detects light. It can be used as a simple method of checking that the optical network is properly connected to the receiver.

The Own Data LED is turned ON when the board has detected its own data returning over the network. The LED can be turned OFF by clearing Bit 0 of the Control and Status register.

## 7.4 Fiber optic connections

In the fiber optic Small Form-factor Pluggable (SFP) interface of the *ibaFOB-R* board, a single-mode SFP or multimode SFP can be installed.

The following table below gives an overview of the cable specification for both singlemode and multimode fibers.

| Specification         | Singlemode                  | Multimode                            |  |

|-----------------------|-----------------------------|--------------------------------------|--|

| Core Diameter         | 8.3 ±1.0 μm                 | 50/62.5 ±3 μm                        |  |

| Cladding Diameter     | 125 ±2 μm                   | 125 ±2 μm                            |  |

| Jacket Outer Diameter | 3.0 mm ±0.1 mm              | 3.0 mm ±0.1 mm                       |  |

| Attenuation           | 0.8 dB/km (max) at 1310 nm  | 4.0 dB/km (max) at 850 nm            |  |

| Bandwidth             | N/A                         | 160 to 300 MHz*km (min) at<br>850 nm |  |

| UL                    | type OFNR, CSA type OFN FT4 | type OFNR, CSA type OFN FT4          |  |

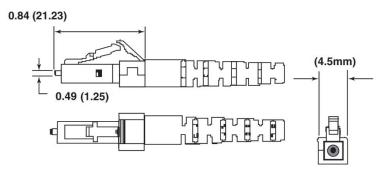

The *ibaFOB-R* board is delivered with a multimode SFP module installed, using LC type fiber optic connectors.

LC type fiber optic connectors:

Dimensions: inches (mm)

## 8 Configuration

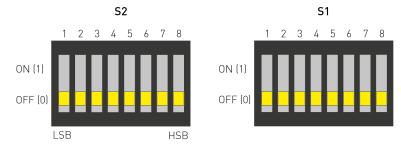

Prior to installing the board, a number of settings must be configured using 2 DIP (dual in-line package) switches S1 and S2 on the *ibaFOB-R* board.

The following illustration shows the arrangement of switches S1 and S2.

Factory defaults of the DIP switches:

## 8.1 Switch S1 configuration

Prior to installing the *ibaFOB-R* board into the host system, switch S1 must be configured for the appropriate mode of operation. Switch S1 controls six functions on the board.

Settings on Switch S1 should only be changed while power is off.

#### Тір

In most cases there is no need to do the S1 configuration. It can therefore remain in the default state with all switches in the OFF state.

- S1 position 1: selects the redundant (ON) or non-redundant (OFF) network transfer mode.

- S1 position 2 reduces the transmission rate of the board onto the network in order to avoid congestion for other network participants (ON). Full transmission bandwidth is available when OFF.

- S1 positions 3 and 4: select the PCI window size for PIO memory accesses. The default (when both switch positions 3 and 4 are OFF) is to use the full installed memory size. The reduced memory window size choices are 64 MB, 16 MB or 2 MB.

- S1 position 5 enables (ON position) or disables the Rogue Master 0 function.

- S1 position 6 enables (ON position) or disables the Rogue Master 1 function.

- S1 position 7: currently reserved (should be left in the OFF position).

- S1 position 8: currently reserved (should be left in the OFF position).

The tables below gives an overview of the S1 settings.

#### Switch S1 configuration settings

| Position 1                         | OFF: non-redundant mode      | Position 2                         | OFF: full transmission bandwidth        |  |

|------------------------------------|------------------------------|------------------------------------|-----------------------------------------|--|

|                                    | ON: redundant mode           |                                    | ON: reduced transmission band-<br>width |  |

| Position 5                         | OFF: disables Rogue Master 0 | Position 6                         | OFF: disables Rogue Master 1            |  |

|                                    | ON: enables Rogue Master 0   | ON: enables Rogue Master           |                                         |  |

| Position 3 and 4 : see table below |                              | Factory Default: Positions 1-8 OFF |                                         |  |

#### Switch S1 PCI Window configuration

| PCI Window Size  | S1 Position 3 | S1 Position 4 |

|------------------|---------------|---------------|

| 256 MB (default) | OFF           | OFF           |

| 64 MB            | ON            | OFF           |

| 16 MB            | OFF           | ON            |

| 2 MB             | ON            | ON            |

## 8.2 Switch S2 configuration

Prior to installing the *ibaFOB-R* in a host system, the desired node ID must be set using switch S2. Each node in the network must have a unique node ID.

Switch S2 corresponds to 8 node ID select signal lines. The 8 node ID select lines permit any binary node ID from 0x00 to 0xFF (255 decimal).

Switch S2 position 1 (on the left!) corresponds to the least significant node ID line and switch S2 position 8 (on the right!) corresponds to the most significant node ID line.

Placing switch S2 in the OFF position sets the binary node ID line low (0), while placing switch S2 in the ON position sets the binary node ID line high (1).

The following table provides examples of possible node IDs.

| S2      | S2                                 | S2     | S2     | S2     | S2     | S2     | S2     | Node ID    |

|---------|------------------------------------|--------|--------|--------|--------|--------|--------|------------|

| Pos. 1  | Pos. 2                             | Pos. 3 | Pos. 4 | Pos. 5 | Pos. 6 | Pos. 7 | Pos. 8 | Hex (Dec.) |

| ON      | ON                                 | ON     | ON     | ON     | ON     | ON     | ON     | 0xFF (255) |

| OFF     | OFF                                | OFF    | OFF    | OFF    | OFF    | OFF    | ON     | 0x80 (128) |

| OFF     | OFF                                | OFF    | OFF    | OFF    | OFF    | ON     | OFF    | 0x40 (64)  |

| OFF     | OFF                                | OFF    | OFF    | OFF    | ON     | OFF    | OFF    | 0x20 (32)  |

| OFF     | OFF                                | OFF    | OFF    | ON     | OFF    | OFF    | OFF    | 0x10 (16)  |

| OFF     | OFF                                | OFF    | ON     | OFF    | OFF    | OFF    | OFF    | 0x8 (8)    |

| OFF     | OFF                                | ON     | OFF    | OFF    | OFF    | OFF    | OFF    | 0x4 (4)    |

| OFF     | ON                                 | OFF    | OFF    | OFF    | OFF    | OFF    | OFF    | 0x2 (2)    |

| ON      | OFF                                | OFF    | OFF    | OFF    | OFF    | OFF    | OFF    | 0x1 (1)    |

| OFF     | OFF                                | OFF    | OFF    | OFF    | OFF    | OFF    | OFF    | 0x0 (0)    |

| Factory | Factory default: positions 1-8 OFF |        |        |        |        |        |        |            |

### 8.2.1 Important remarks before installation

Observe the following notes when configuring switches S1 and S2:

#### Note

Each Reflective Memory module on your Reflective Memory network must have a unique node ID to identify itself. So before setting the node ID by switch S2, check the node ID of all other participants on the network. There is no inherent detection of duplicate nodes on a network!

#### Note

ALL nodes on the ring MUST be configured for the SAME transfer mode, either redundant or non-redundant transfer mode. A mismatch of this setting will result in certain packets being removed from the ring, and that data will be lost.

Note

1

No more than one node on the ring should be configured with Rogue Master 0 enabled. Certain packets will be removed from the ring when two or more nodes are configured with Rogue Master 0 enabled, and that data will be lost.

#### Note

No more than one node on the ring should be configured with Rogue Master 1 enabled. Certain packets will be removed from the ring when two or more nodes are configured with Rogue Master 1 enabled, and that data will be lost.

## 9 Configuration in ibaPDA

This manual describes all the features of the *ibaFOB-R* board when used in the *ibaPDA* system, including additional diagnostics and troubleshooting information.

#### Other documentation

For configuration in *ibaPDA*, please refer to manual *ibaPDA-Interface-Reflective-Memory*.

For data acquisition via Reflective Memory with *ibaPDA*, the interface license *ibaPDA-Interface-Reflective-Memory* (31.001220) has to be purchased separately (as in the past with ABACO and former Reflective Memory boards).

## **10** System integration

#### Note

This chapter is intended for system integrators who want to use the *ibaFOB-R* board in their own automation or embedded system.

For users of the *ibaFOB-R* board together with *ibaPDA*, this detailed information is less relevant.

The following sections describe the functionality of the *ibaFOB-R* board. A description of the major sub-circuits and their operation is included.

This section will also occasionally mention Control and Status registers related to operations. To see a detailed description of these Control and Status registers please refer to chapter **7** *Pro- gramming requirements,* page 26.

## **10.1** Basic functionality and operation

Each node in the Reflective Memory network is interconnected using fiber-optic cables in a daisy chain loop. The transmitter of the first board must be connected to the receiver of the second board. The transmitter of the second board is connected to the receiver of the third, and so on, until the loop is completed back at the receiver of the first board.

Alternatively, any node can be connected to the ring network using one or more Reflective Memory hubs.

It is important that the ring network is complete (i.e., every receiver and transmitter must be connected). Each node must have a unique node ID, which is set using switch S2 (i.e. no two nodes should have the same node ID). The order of the node IDs is unimportant.

A transfer of data over the network is initiated by a write from the host system to the onboard RAM memory. The write can be as simple as a PIO target write, or it can be due to a DMA cycle by the resident DMA engine.

While the write to the RAM is occurring, circuitry on the *ibaFOB-R* board automatically writes the data and other pertinent information into the transmit FIFO.

From the transmit FIFO, the transmit circuit retrieves the data and puts it into a variable length packet of 4 to 64 bytes that is transmitted over the fiber-optic interface to the receiver of the next board. The receiver then checks the packet for errors. When the error free data is received, the receive circuit stores the data in the board's receive FIFO. From the receive FIFO, another circuit writes the data into the local onboard RAM at the same relative location in memory as the originating node.

This circuit also simultaneously routes the data into the board's own transmit FIFO. From there, the process is repeated until the data returns to the receiver of the originating node. At the originating node, the data packet is removed from the network.

## **10.2** ibaFOB-R hardware registers

Users who want to go beyond the standard read write operations, must understand and manipulate bits within three register sets. The three register sets are:

- PCI Configuration Registers, see **7** PCI Configuration Registers, page 27

- Local Configuration Registers, see **7** Local Configuration Registers, page 35

- RFM Control and Status Registers, see **7** RFM Control and Status Registers, page 38

#### **PCI Configuration Registers**

This set of registers is predefined by the PCI Local Bus Specification and is standard for all PCI and PCI Express devices. This register set contains the Vendor ID, Device ID, Subsystem Vendor ID and Base Address registers. The PCI Configuration Registers are first initialized and then modified as needed by the PCI bus system BIOS. The register set is rarely altered by the user, but the ability to read these registers, particularly the Base Address Registers, will be necessary to locate the other two sets of registers.

#### **Local Configuration Registers**

Base Address Register 0 contains the starting address for the Local Configuration Registers. Some Local Configuration Registers pertinent to the *ibaFOB-R*'s operation include the Interrupt Control and Status Register (INTCSR) and the DMA Control Registers.

#### **RFM Control and Status Registers**

The RFM Control and Status Registers implement the functions unique to the *ibaFOB-R* Reflective Memory board. These functions include RFM operation status, detailed control of the RFM sources for the PCI interrupt, and network interrupt access. These registers are accessed starting at the address contained in Base Address Register 2.

## **10.3** Reflective Memory RAM on ibaFOB-R

The *ibaFOB-R* board is available with 256 MB of onboard Reflective Memory RAM.

The RAM starts at the location specified in Base Address Register 3.

The offset address range is 0 to 0xFFFFFFF for 256 MB.

This address range can be limited by setting the S1 switch accordingly, see chapter **7** Switch S1 configuration, page 18.

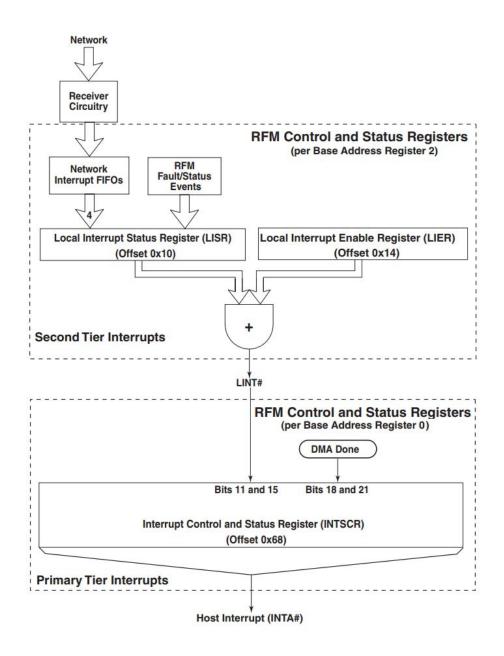

## **10.4** Interrupt generation

The *ibaFOB-R* board has a single interrupt output on the PCIe bus.

The interrupt can be generated as a legacy INTA# message level interrupt or as an MSI or MSI-X event interrupt when enabled by the system software.

One or more events on the *ibaFOB-R* board can cause the interrupt. The sources of the interrupt can be individually enabled and monitored through several registers. The interrupt circuitry of the *ibaFOB-R* board is arranged in two tiers.

The primary tier of interrupts is enabled and monitored by the Local Configuration Register's INTCSR at offset 0x68. The sources for the primary tier interrupts are:

- 1. DMA Done

- 2. Local Interrupt Input

The primary tier interrupt source (1) can be used to report the end of a DMA transfer and it must be configured in the DMA registers. The other primary tier interrupt source (2) is the Local Interrupt Input.

All secondary tier interrupts are funneled through the Local Interrupt Input. Second tier interrupts include several operational status bits, faults, and network interrupts. The second tier interrupts are selected and monitored through the two RFM Control and Status Registers referred to as the Local Interrupt Status Register (LISR) and the Local Interrupt Enable Register (LIER).

For a detailed description of these two registers refer to chapter. **7** *RFM Control and Status Registers*, page 38

A block diagram of the interrupt circuit is shown in the following figure.

## **10.5** Network interrupts

The *ibaFOB-R* board is capable of passing interrupt packets, as well as data packets, over the network. The network interrupt packets can be directed to a specific node or broadcast globally to all other nodes on the network. Each network interrupt packet contains the sender's node ID, the destination node ID, the interrupt type and 32 bits of user defined data.

The types of network interrupts include four general purpose interrupts and a reset node request interrupt. Node specific interrupts are sent by configuring three RFM Control and Status registers. Each receiving node evaluates the interrupt packets as they pass through. If a general purpose interrupt is directed to that node, then the sender's node ID is stored in the appropriate Sender ID FIFO (one of four). Each Sender ID FIFO is at least 127 locations deep. The accompanying data will be stored in a companion data FIFO.

If enabled through the LISR, LIER and INTCSR registers, any of the network interrupts can also generate a host PCI interrupt at each receiving node.

The reset node request interrupt is not stored in a FIFO like the four general purpose interrupts. Furthermore, it does not cause an immediate reset of the board. Instead, it sets a bit in the LISR register, which will result in a PCI interrupt if enabled. The actual board reset should be performed by the host system in an orderly fashion. However, the user application could use this network interrupt for any purpose.

## 10.6 Redundant Transfer mode

The *ibaFOB-R* board is capable of operating in a redundant transfer mode. The board is configured for redundant mode when switch S1 position 1 is in the ON position. In the redundant transfer mode, each generated packet transfers twice, regardless of the packet size. The receiving circuitry of each node on the network evaluates each of the redundant transfers. If no errors are detected in the first transfer, it is used to update the onboard memory and the second transfer is discarded. However, if the first transfer contains an error, the second transfer is used to update the onboard memory provided it has no transmission errors. If errors are detected in both transfers, the transfers will not be used and the data is completely removed from the network.

Redundant transfer mode reduces the chance that any data is dropped from the network. However, the redundant transfer mode also reduces the network data transfer rate. The single DWord (Double-word = 4 byte) transfer rate drops from the non-redundant rate of 43 MB/s to approximately 20 MB/s. The 16 DWord (64 byte) transfer rate drops from the non-redundant rate of 170 MB/s to the redundant rate of 85 MB/s.

## **10.7** Rogue Packet Removal Operation mode

A rogue packet is a packet that does not belong to any node on the network. Recalling the basic operation of Reflective Memory, one node originates a packet on the network in response to a memory write from the host. The packet is transferred around the network to all nodes until it returns to the originating node. It is a requirement that the originating node removes the packet from the network. If, however, the packet is erroneously altered as it passes through another node, or if the originating node begins to malfunction, then the originating node may fail to

recognize the packet as its own and will not remove it from the network. In this case, the packet will continue to traverse the network as a "rogue packet."

Rogue packets are extremely rare. A rogue packet could be created when turning a node's power on or off while connected to an optical Hub. It could also occur when connecting or disconnecting fiber cables. A rogue packet might be created if any node in the network overflows a network FIFO. Their existence could indicate a malfunctioning board due to true component failure, or due to operation in an overly harsh environment. Normally, the solution is to isolate and replace the malfunctioning board and/or improve the environment. However, some users prefer to tolerate sporadic rogue packets rather than halt the system for maintenance provided the rogue packets are removed from the network.

To provide tolerance for rogue packet faults, the *ibaFOB-R* board contains circuitry that allows it to operate as one of two Rogue Masters. A rogue master marks each packet as it passes through from another node. If the same packet returns to the rogue master a second time, the Rogue Master recognizes that it is a rogue packet and removes it from the network (after the rogue packet has affected every node). When a rogue packet is detected, a rogue packet fault flag is set in the LISR. The assertion of the rogue packet fault bit may optionally assert a PCI interrupt to inform the host that the condition exists. Two rogue masters, Rogue Master 0 and Rogue Master 1, are provided to cross check each other. Rogue Master 0 is enabled by placing switch S1 position 5 in the ON position. Rogue Master 1 is enabled by placing switch S1 position 6 in the ON position. Just as two boards in a network should not have the same node ID, two boards in the same network should not be set as the same Rogue Master. Otherwise, one of the two will erroneously remove packets marked by the other.

## 10.8 Programming requirements

Basic target write and read operations of the *ibaFOB-R-* board require little or no software.

The board powers up in a functional mode. The user will need to access the PCI Configuration registers (Base Address Register 0, 2 and 3) to learn where the system BIOS has located the other register sets and the Reflective Memory.

The location of the register sets and the Reflective Memory varies from system to system and can even vary from slot to slot within a system.

For operations beyond the basic setup, such as enabling or disabling interrupts or performing DMA cycles, the user must know the specific bit assignments of the registers within the three register sets. That information is provided in this chapter.

The three register sets are:

- PCI Configuration Registers

- Local Configuration Registers

- RFM Control and Status Registers

## **10.8.1** PCI Configuration Registers

The PCI Configuration registers are located in 256 bytes of the PCI Configuration Space, which follows a template defined by the PCI Specification.

Although the PCI Configuration registers are accessible at all times, they are rarely altered by the user application. In most cases these are configured by system software.

| Address (Hex)                                                                                                            | 3124                       | 2316            | 158                 | 70                      |  |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|---------------------|-------------------------|--|

| 00                                                                                                                       | Devi                       | ce ID           | Vendor ID           |                         |  |

| 04                                                                                                                       | Status F                   | Register        | Command Register    |                         |  |

| 08                                                                                                                       |                            | Class Code      |                     | Revision ID             |  |

| 0C                                                                                                                       | BIST*                      | Header Type     | Latency Timer*      | Cache Line Size*        |  |

| 10                                                                                                                       |                            | Base Addres     | ss Register 0       |                         |  |

| 14                                                                                                                       |                            | Base Addres     | s Register 1*       |                         |  |

| 18                                                                                                                       |                            | Base Addres     | ss Register 2       |                         |  |

| 1C                                                                                                                       |                            | Base Addres     | ss Register 3       |                         |  |

| 20                                                                                                                       |                            | Base Addres     | s Register 4*       |                         |  |

| 24                                                                                                                       |                            | Base Addres     | s Register 5*       |                         |  |

| 28                                                                                                                       |                            | Cardbus C       | IS Pointer*         |                         |  |

| 2C                                                                                                                       | Subsys                     | tem ID          | Subsystem           | Vendor ID               |  |

| 30                                                                                                                       |                            | Expansion RON   | I Base Address*     |                         |  |

| 34                                                                                                                       |                            | Reserved*       |                     | Capabilities<br>Pointer |  |

| 38                                                                                                                       |                            | Reser           | rved*               |                         |  |

| 3C                                                                                                                       | Max_Lat*                   | Min_Gnt*        | Interrupt Pin       | Interrupt Line          |  |

| 4047                                                                                                                     | Р                          | ower Management | Capability Structur | e                       |  |

| 484F                                                                                                                     |                            | MSI Capabili    | ity Structure       |                         |  |

| 505F                                                                                                                     |                            | Reser           | rved*               |                         |  |

| 609B                                                                                                                     | PCIe Capability Structure  |                 |                     |                         |  |

| 9CA7                                                                                                                     | MSI-X Capability Structure |                 |                     |                         |  |

| A8FF                                                                                                                     | Reserved*                  |                 |                     |                         |  |

| Cells marked with * indicate reserved or non-applicable registers for <i>ibaFOB-R</i> (value unde-<br>fined after reset) |                            |                 |                     |                         |  |

#### PCI Configuration Registers

## PCI Configuration ID Registers (Offset 0x00)

| Bit   | Description                       | Read | Write | Value after<br>PCI Reset |

|-------|-----------------------------------|------|-------|--------------------------|

| 15:0  | Vendor ID                         | Yes  | No    | 0x167F                   |

|       | Identifies manufacturer of device |      |       | = iba AG                 |

| 31:16 | Device ID                         | Yes  | No    | 0x5565                   |

|       | Identifies particular device      |      |       |                          |

#### PCI Command Register (Offset 0x04)

| Bit | Description                                                                                                                 | Read | Write | Value after<br>PCI Reset * |

|-----|-----------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------|

| 0   | I/O Space                                                                                                                   | Yes  | Yes   | 0                          |

|     | Writing a one (1) allows the device to respond to I/O Space accesses.                                                       |      |       |                            |

|     | Writing a zero (0) disables the device from re-<br>sponding to I/O Space accesses                                           |      |       |                            |

| 1   | Memory Space                                                                                                                | Yes  | Yes   | 0                          |

|     | Writing a one (1) allows device to respond to Memory Space accesses.                                                        |      |       |                            |

|     | Writing a zero (0) disables the device from re-<br>sponding to Memory Space accesses.                                       |      |       |                            |

| 2   | Bus Master Enable                                                                                                           | Yes  | Yes   | 0                          |

|     | Writing a one (1) allows the device to behave as<br>a bus master (required for DMA and for sending<br>MSI/MSI-X interrupts) |      |       |                            |

|     | Writing a zero (0) disables the device from generating bus master accesses.                                                 |      |       |                            |

| 3   | Special Cycle Enable                                                                                                        | Yes  | No    | 0                          |

|     | Not applicable to PCI Express                                                                                               |      |       |                            |

| 4   | Memory Write and Invalidate                                                                                                 | Yes  | No    | 0                          |

|     | Not applicable to PCI Express                                                                                               |      |       |                            |

| 5   | VGA Palette Snoop                                                                                                           | Yes  | No    | 0                          |

|     | Not applicable to PCI Express                                                                                               |      |       |                            |

| 6   | Parity Error Response                                                                                                       | Yes  | Yes   | 0                          |

|     | Report PCIe poisoned completion TLP when en-<br>abled (1) in the PCI Status Register                                        |      |       |                            |

| 7   | Wait Cycle Control                                                                                                          | Yes  | No    | 0                          |

|     | Not applicable to PCI Express                                                                                               |      |       |                            |

| Bit      | Description                                                                                                                  | Read      | Write      | Value after<br>PCI Reset * |

|----------|------------------------------------------------------------------------------------------------------------------------------|-----------|------------|----------------------------|

| 8        | SERR# Enable                                                                                                                 | Yes       | Yes        | 0                          |

|          | Report PCIe Fatal and Non-fatal Errors when en-<br>abled (1)                                                                 |           |            |                            |

| 9        | Fast Back-to-Back Transaction Enable                                                                                         | Yes       | No         | 0                          |

|          | Not applicable to PCI Express                                                                                                |           |            |                            |

| 10       | Interrupt Disable                                                                                                            | Yes       | Yes        | 0                          |

|          | When set (1) disables the <i>ibaFOB-R</i> from sending legacy interrupt messages (INTA#).                                    |           |            |                            |

|          | This bit has no influence on MSI/MSI-X in-<br>terrupts. When cleared (0) INTA# interrupt<br>messages are generated normally. |           |            |                            |

| 15:11    | Reserved                                                                                                                     | Yes       | No         | 0                          |

| *Note:   | This register will likely be altered by system software                                                                      | during th | e system b | oot process                |

| (e.g. 0) | :0106).                                                                                                                      |           |            |                            |

## PCI Status Register (Offset 0x06)

| Bit | Description                                                                                                                                                     | Read | Write   | Value after<br>PCI Reset |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|--------------------------|

| 2:0 | Reserved                                                                                                                                                        | Yes  | No      | 0x0                      |

| 3   | Interrupt Status                                                                                                                                                | Yes  | No      | 0                        |

|     | Set by the <i>ibaFOB-R</i> board when the function would normally assert an interrupt pin, regard-less of interrupt disable bit state.                          |      |         |                          |

| 4   | New Capabilities Functions Support                                                                                                                              | Yes  | No      | 1                        |

|     | Hardwired to a one (1). The <i>ibaFOB-R</i> imple-<br>ments a capabilities list.                                                                                |      |         |                          |

| 5   | 66 MHz Capable                                                                                                                                                  | Yes  | No      | 0                        |

|     | Not applicable to PCI Express                                                                                                                                   |      |         |                          |

| 6   | Reserved                                                                                                                                                        | Yes  | No      | 0                        |

| 7   | Fast Back-to-Back Capable                                                                                                                                       | Yes  | No      | 0                        |

|     | Not applicable to PCI Express                                                                                                                                   |      |         |                          |

| 8   | Master Data Parity Error                                                                                                                                        | Yes  | Yes/Clr | 0                        |

|     | When set (1), indicates the <i>ibaFOB-R</i> board has detected a poisoned completion, but only if the Parity Error Response bit is set in the Command Register. |      |         |                          |

| Bit  | Description                                                                                                                                                      | Read | Write   | Value after<br>PCI Reset |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|--------------------------|

| 10:9 | DEVSEL# Timing                                                                                                                                                   | Yes  | No      | 0                        |

|      | Not applicable to PCI Express                                                                                                                                    |      |         |                          |

| 11   | Signaled Target Abort                                                                                                                                            | Yes  | Yes/Clr | 0                        |

|      | When set (1), indicates the <i>ibaFOB-R</i> board has signaled a Completer Abort.                                                                                |      |         |                          |

|      | Writing a one (1) clears this bit to zero (0).                                                                                                                   |      |         |                          |

| 12   | Received Target Abort                                                                                                                                            | Yes  | Yes/Clr | 0                        |

|      | When set (1), indicates the <i>ibaFOB-R</i> board has received a Completer Abort response.                                                                       |      |         |                          |

|      | Writing a one (1) clears this bit to zero (0).                                                                                                                   |      |         |                          |

| 13   | Received Master Abort                                                                                                                                            | Yes  | Yes/Clr | 0                        |

|      | When set (1), indicates the <i>ibaFOB-R</i> board has received an Unsupported Request response                                                                   |      |         |                          |

|      | Writing a one (1) clears this bit to zero (0).                                                                                                                   |      |         |                          |

| 14   | Signaled Signal System Error                                                                                                                                     | Yes  | Yes/Clr | 0                        |

|      | When set (1), indicates the <i>ibaFOB-R</i> board has<br>sent an ERR_FATAL or ERR_NONFATAL message<br>if the SERR# Enable is set in the Command<br>Register.     |      |         |                          |

|      | Writing a one (1) clears this bit to zero (0).                                                                                                                   |      |         |                          |

| 15   | Detected Parity Error                                                                                                                                            | Yes  | Yes/Clr |                          |

|      | When set (1), indicates the <i>ibaFOB-R</i> board has detected a poisoned TLP, regardless of the state of the Parity Error Response bit in the Command Register. |      |         |                          |

|      | Writing a one (1) clears this bit to zero (0)                                                                                                                    |      |         |                          |

## PCI Revision ID Register (Offset 0x08)

| Bit | Description                  | Read | Write | Value after<br>PCI Reset |

|-----|------------------------------|------|-------|--------------------------|

| 7:0 | Revision ID                  | Yes  | No    | Current Rev#             |

|     | Revision number of the board |      |       |                          |

#### PCI Class Code Register (Offset 0x09)

| Bit                                                                                                                       | Description                                                | Read | Write | Value after<br>PCI Reset |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|-------|--------------------------|

| 7:0                                                                                                                       | <b>Register Level Programming Interface.</b> None defined. | Yes  | No    | 0x0                      |

| 15:8                                                                                                                      | Subclass Code                                              | Yes  | No    | 0x80                     |

| 23:16                                                                                                                     | Base Class Code                                            | Yes  | No    | 0x02                     |

| Base Class Code of 0x02 equals <i>Network Controller</i> . Subclass Code of 0x80 equals <i>Other Network Controller</i> . |                                                            |      |       |                          |

#### PCI Header Type Register (Offset 0x0E)

| Bit | Description                                  | Read | Write | Value after |

|-----|----------------------------------------------|------|-------|-------------|

|     |                                              |      |       | PCI Reset   |

| 6:0 | Configuration Layout Type                    | Yes  | No    | 0x0         |

|     | Zero (0) indicates an Endpoint device.       |      |       |             |

| 7   | Header Type                                  | Yes  | No    | 0x0         |

|     | Zero (0) indicates a single function device. |      |       |             |

PCI Base Address Register 0 contains the starting address for memory mapped access to the Local Configuration Registers. The value in this register is configured by the system BIOS.

| PCI Base Address Register 0 (Offset 0x10) | [Local Configuration Registers] |

|-------------------------------------------|---------------------------------|

|-------------------------------------------|---------------------------------|

| Bit    | Description                                                        | Read        | Write     | *Value after<br>PCI Reset |

|--------|--------------------------------------------------------------------|-------------|-----------|---------------------------|

| 0      | Memory Space Indicator                                             | Yes         | No        | 0                         |

|        | 0 indicates the register maps into Memory Space.                   |             |           |                           |

| 2:1    | Register Location                                                  | Yes         | No        | 00                        |

|        | 00 - Locate anywhere in 32-bit Memory Address<br>Space             |             |           |                           |

| 3      | Prefetchable Indicator                                             | Yes         | No        | 0                         |

|        | 0 indicates non-prefetchable                                       |             |           |                           |

| 8:4    | Memory Base Address                                                | Yes         | No        | 0x0                       |

|        | Hardcoded to 0x0 to indicate a size of 512 bytes                   |             |           |                           |

| 31:9   | Memory Base Address                                                | Yes         | Yes       | 0x0                       |

|        | Memory Base Address for access to Local<br>Configuration registers |             |           |                           |

| *Note: | This register will be altered by the system BIOS durir             | ng the syst | em boot p | process.                  |

PCI Base Address Register 1 is not used in the *ibaFOB-R* board.

PCI Base Address Register 2 contains the starting address for memory mapped access to the RFM Control and Status Registers. The value in this register is configured by the system BIOS.

| Bit    | Description                                                        | Read         | Write     | *Value after<br>PCI Reset |

|--------|--------------------------------------------------------------------|--------------|-----------|---------------------------|

| 0      | Memory Space Indicator                                             | Yes          | No        | 0                         |

|        | 0 indicates the register maps into Memory Space.                   |              |           |                           |

| 2:1    | Register Location                                                  | Yes          | No        | 00                        |

|        | 00 - Locate anywhere in 32-bit Memory Address<br>Space             |              |           |                           |

| 3      | Prefetchable Indicator                                             | Yes          | No        | 0                         |

|        | 0 indicates non-prefetchable                                       |              |           |                           |

| 6:4    | Memory Base Address                                                | Yes          | No        | 0x0                       |

|        | Hardcoded to 0x0 to indicate a size of 128 bytes                   |              |           |                           |

| 31:7   | Memory Base Address                                                | Yes          | Yes       | 0x0                       |

|        | Memory Base Address for access to RFM Control and Status registers |              |           |                           |

| *Note: | This register will be altered by the system BIOS durin             | ng the syste | em boot p | rocess.                   |

#### PCI Base Address Register 2 (Offset 0x18) [RFM Control and Status]

PCI Base Address Register 3 contains the starting address for memory mapped access to the Reflective Memory RAM. The value in this register is configured by the system BIOS. It depends on the settings of S1 switch positions 3 and 4. The address offset range is:

- 0x0 to 0x01FFFFF for the 2 MB window setting,

- 0x0 to 0x0FFFFFF for the 16 MB window setting,

- 0x0 to 0x3FFFFFF for the 64 MB window setting,

- 0x0 to 0xFFFFFF for 256 MB if windowing is deactivated by S1

#### PCI Base Address Register 3 (Offset 0x1C) [Reflective Memory RAM]

| Bit | Description                                                                        | Read | Write | *Value after<br>PCI Reset |

|-----|------------------------------------------------------------------------------------|------|-------|---------------------------|

| 0   | Memory Space Indicator<br>0 indicates the register maps into Memory<br>Space.      | Yes  | No    | 0                         |

| 2:1 | <b>Register Location</b><br>00 - Locate anywhere in 32-bit Memory Address<br>Space | Yes  | No    | 00                        |

Issue 1.0

32

| Bit      | Description                                                | Read        | Write      | *Value after<br>PCI Reset |

|----------|------------------------------------------------------------|-------------|------------|---------------------------|

| 3        | Prefetchable Indicator                                     | Yes         | No         | 0                         |

|          | 0 indicates non-prefetchable                               |             |            |                           |

| 31:4     | Memory Base Address.                                       | Yes         | Yes        | 0x0                       |

|          | Memory Base Address for access to Reflective<br>Memory RAM |             |            |                           |

|          | (size depending on windowing as explained above)           |             |            |                           |

| *Note: T | nis register will be altered by the system BIOS durin      | g the syste | em boot pi | ocess.                    |

PCI Base Address Register 4 and 5 are not used in the *ibaFOB-R* board.

#### PCI Subsystem Vendor ID Register (Offset 0x2C)

| Bit  | Description         | Read | Write | Value after<br>PCI Reset |

|------|---------------------|------|-------|--------------------------|

| 15:0 | Subsystem Vendor ID | Yes  | No    | 0x167F                   |

|      |                     |      |       | = iba AG                 |

#### PCI Subsystem ID Register (Offset 0x2E)

| Bit  | Description  | Read | Write | Value after<br>PCI Reset |

|------|--------------|------|-------|--------------------------|

| 15:0 | Subsystem ID | Yes  | No    | 0x5565                   |

#### PCI Capabilities Pointer Register (Offset 0x34)

| Bit | Description                                                                                                         | Read | Write | Value after<br>PCI Reset |

|-----|---------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------|

| 7:0 | Capabilities Pointer                                                                                                | Yes  | No    | 0x40                     |

|     | Offset into PCI Configuration Space for the lo-<br>cation of the first item in the PCI Capabilities<br>Linked List. |      |       |                          |

#### PCI Interrupt Line (Offset 0x3C)

| Bit       | Description                                                                                                                                                             | Read        | Write      | *Value after<br>PCI Reset |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|---------------------------|

| 7:0       | Interrupt Line Routing Value                                                                                                                                            | Yes         | Yes        | 0x0                       |

|           | Value used by the operating system to indicate<br>to which input of the system interrupt controller<br>the (virtual) interrupt line of the device is con-<br>nected to. |             |            |                           |

| *Note: Tł | nis register will be altered by the system BIOS durin                                                                                                                   | g the syste | em boot pi | rocess.                   |

#### PCI Interrupt Pin (Offset 0x3D)

| Bit | Description                                                                      | Read | Write | Value after<br>PCI Reset |

|-----|----------------------------------------------------------------------------------|------|-------|--------------------------|

| 7:0 | Interrupt Pin Register                                                           | Yes  | No    | 0x1                      |

|     | Indicates which legacy interrupt pin the device uses.                            |      |       |                          |

|     | 1 = INTA# ( <i>ibaFOB-R</i> only uses INTA# or message based MSI(-X) interrupts) |      |       |                          |

The *ibaFOB-R* board supports the following 4 standardized PCI Capability structures.

In general, these registers are managed by system software.

#### Capability structures

| PCI Configuration | Capability | Description                                               |

|-------------------|------------|-----------------------------------------------------------|

| space address     | ID         |                                                           |

| 0x400x47          | 0x01       | The Power Management Capability Structure                 |

| 0x480x4F          | 0x05       | The MSI (Message Signaled Interrupt) Capability Structure |

| 0x600x9B          | 0x10       | The PCI Express Capability Structure                      |

| 0x9C0xA7          | 0x11       | The MSI-X (extended MSI) Capability Structure             |

Тір

To find more detailed information about the various capability structures in PCI devices, you can refer to the PCI Local Bus Specification, which is maintained by the PCI-SIG (PCI Special Interest Group). The PCI Local Bus Specification outlines the standards and protocols for PCI devices, including the structure and usage of capability structures.

## 10.8.2 Local Configuration Registers

The Local Configuration Registers are accessible at the address specified by the value in Base Address Register 0. The offsets are specified below.

| Offset from Base<br>Address | Register Name                         | Writable |

|-----------------------------|---------------------------------------|----------|

| 0x00-0x67                   | Reserved                              | N/A      |

| 0x68                        | Interrupt Control and Status (INTCSR) | Yes      |

| 0x6C-0x83                   | Reserved                              | N/A      |

| 0x84                        | DMA PCI Address                       | Yes      |

| 0x88                        | DMA RFM Address                       | Yes      |

| 0x8C                        | DMA Transfer Size                     | Yes      |

| 0x90                        | DMA Direction                         | Yes      |

| 0x94-0xA7                   | Reserved                              | N/A      |

| 0xA8                        | DMA Control and Status (DMACSR)       | Yes      |

| 0xAC-0xB3                   | Reserved                              | N/A      |

| 0xB4                        | DMA PCI Upper Address                 | Yes      |

| 0xB8-0xEF                   | Reserved                              | N/A      |

| 0xF0                        | RFM Window Mask                       | No       |

| 0xF4                        | RFM Window Base Address               | Yes      |

| 0xF8-0x1FF                  | Reserved                              | N/A      |

Local Configuration and DMA Control Registers

#### Interrupt Control and Status Register [BAR0.0x68]

Note: only relevant bits are described, other register bits are reserved (write zero to them)

| Bit | Description                                                                          | Read | Write | Value after<br>PCI Reset |

|-----|--------------------------------------------------------------------------------------|------|-------|--------------------------|

| 8   | PCI Interrupt Enable                                                                 | Yes  | Yes   | 1                        |

|     | Functions as global interrupt enable. Bit must be set to enable PCI interrupts.      |      |       |                          |

| 11  | Local Interrupt Enable                                                               | Yes  | Yes   | 0                        |

|     | Enables the local interrupt sources (RFM inter-<br>rupts) to assert a PCI interrupt. |      |       |                          |

| 15  | Local Interrupt Active                                                               | Yes  | No    | 0                        |

|     | When set (1) indicates the Local interrupt is active.                                |      |       |                          |

| Bit | Description                                                                     | Read | Write | Value after<br>PCI Reset |

|-----|---------------------------------------------------------------------------------|------|-------|--------------------------|

| 18  | DMA Interrupt Enable                                                            | Yes  | Yes   | 0                        |

|     | Enables the DMA interrupt to assert a PCI inter-<br>rupt.                       |      |       |                          |

|     | Writing a zero (0) disables the DMA interrupt and it also clears the interrupt. |      |       |                          |

| 21  | DMA Interrupt Active                                                            | Yes  | No    | 0                        |

|     | When set (1) indicates the DMA interrupt is active (DMA transfer has finished). |      |       |                          |

#### DMA PCI Address Register [BAR0.0x84]

| Bit  | Description                                                                                                         | Read | Write | Value after<br>PCI Reset |

|------|---------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------|

| 31:0 | <b>DMA PCI Address Register</b><br>Indicates from where in PCI Memory space DMA<br>transfers (read or write) start. | Yes  | Yes   | 0                        |

|      | The address can be aligned to any byte boundary.                                                                    |      |       |                          |

|      | Note: Register BAR0.0xB4 must be set to zero for 32 bit PCI addresses.                                              |      |       |                          |

#### DMA RFM Address Register [BAR0.0x88]

| Bit   | Description                                                                                                                                                                | Read | Write | Value after<br>PCI Reset |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------|

| 27:0  | DMA RFM Address Register<br>Indicates from where in Reflective Memory<br>space DMA transfers (read or write) start.<br>The address can be aligned to any byte<br>boundary. | Yes  | Yes   | 0                        |

| 31:28 | Reserved                                                                                                                                                                   | Yes  | No    | 0                        |

## DMA Transfer Size Register [BAR0.0x8C]

| Bit   | Description                                                                                      | Read | Write | Value after<br>PCI Reset |

|-------|--------------------------------------------------------------------------------------------------|------|-------|--------------------------|